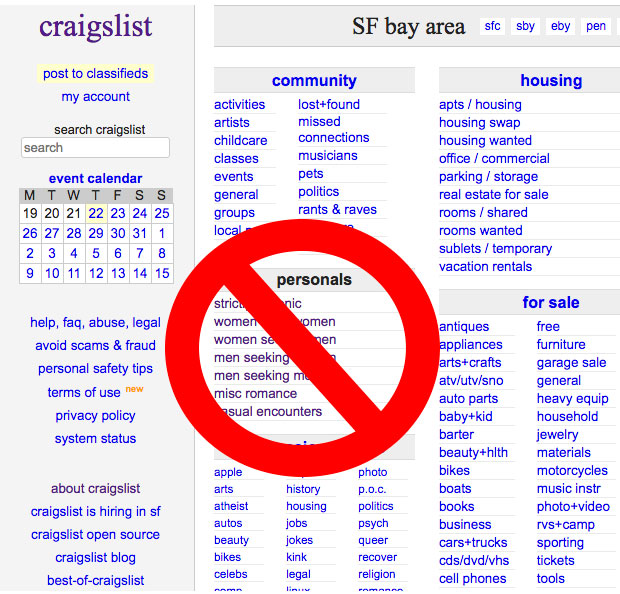

The quantity of those people who are flocking to Fort Worth for Fort Worth craps online is extremely high. The substantial amount of those who are rushing to Fort Worth for Fort Worth craps is a result of the multitude of people who visit Fort Worth every year. This too indicates that there are numerous people in Fort Worth who wish to consider this game as well as the casino houses. If you don’t get that ideal match, at least you will have fun, the Fort Worth craps online Personals have certainly made it easier for people to find their ideal match, and even.

The best thing about the sites is that you can find women seeking men in Fort Worth, and men seeking women in Fort Worth, or just women seeking dates in Fort Worth. There exists a good number of girls trying to find gentlemen within this town along with males seeking females, along with the online dating site is definitely one of the best methods to meet the type of female or man you want. There are various benefits of the web dating internet site in comparison to the traditional strategy for searching for the appropriate form of lover in Fort Worth.

The initial good thing about the web based dating is comfort. Individuals who are looking for days in Fort Worth are now able to use the internet to identify a possible companion. The net is always obtainable in Fort Worth, and even when you are on trip, you may still search on the internet. Because you can choose a probable lover going online is amongst the most significant great things about the web based dating. One of the disadvantages of using the web to find a date in Fort Worth is that you dfw casual encounters cannot see the person face to face.

free hookups near me

The second advantage of the online dating site Fort Worth is that you can view the Personals of all the members of the site at the same time. This allows you to compare them next to each other for the kind of person you are looking for. You can read the Personals and decide whether they seem to be of an interest to you before contacting them. You do not need to spend a lot of time and money to find a date in Fort Worth. That is the beauty of the web.

It is very inexpensive compared to conventional dating services. That’s the third advantage of the dating service Fort Worth craigslist. When considering prices billed by the hotels, dating firms and dining establishments, you might know that an evening in Fort Worth is actually less expensive than a dinner at your house. If you are looking for romance, you will probably have to part with quite a bit of money. However, the service of the dating site is ideal for those on a budget.

It offers a wide variety of choices. That’s the fourth advantage of the free web dating service in Fort Worth. You can choose from the most famous cities of the usa in addition to a few of the less popular destinations like Connecticut and Massachusetts. Furthermore, you can search for folks based on how old they are, sex and ethnicity. This is among the most significant and a lot complete on the web dating services that may be free of charge in the present day.

Craigslist Dating Fort Worth

It provides an interactive environment where you can meet new people. That is another advantage of the Fort Worth Craigslist dating site. You can actually make your personal user profile, that contains your entire details and preferences. If you are looking for romantic endeavors or camaraderie it is possible to look through 1000s of information. Meeting individuals on the web has never ever been this straightforward. If you want to meet new people, you will certainly enjoy the experience of meeting Casual Encounters at the free web dating site Fort Worth personals.

The next task is so that you can visit the Fort Worth Craigslist dating internet site and register. Once registered, you could make your personal account that can contain each of the information you need necessary for the associates. This will help you choose the right sort of Casual Encounters people and allow you to pick these people to meet with your required personal preferences. Whether or not you are looking for older residing, large bright white body or simple thin entire body you are going to definitely look for a perfect personals.